## **CN-7**

CN-7 Testing of COP400 Family Devices

Literature Number: SNOA631

# Testing of COP400 Family Devices

National Semiconductor COP Note 7 April 1991

esting of COP400 Family Device

#### **Table of Contents**

1.0 INTRODUCTION

#### 2.0 PHILOSOPHY

#### 3.0 BUILT-IN TEST FEATURES

3.1 Sync between DUT and Tester

3.2 Internal Logic Test

3.3 RAM Test

3.4 ROM Dump

This note will provide some insight into the test mode, the mechanics of testing, and the philosophy of how to implement a test of the COP-400 microcontrollers. Other than the obvious, (verifying that the part meets the specifications), the reason for the test must be considered. Somewhat different criteria may hold, depending on the objective. The manufacturer wafer sort or final test can differ from an incoming inspection at the user's plant, or a field reject test. The first two tests have limited interest as this is not a justification of the testing done on the part during manufacture. Rather, this is a guide for those doing user functional test-ind.

#### **1.0 INTRODUCTION**

Since the introduction of the very first semiconductor devices, testing has been a major problem and expense in their production and use. As the complexity has risen, testing has become a more significant factor. With today's single chip microcontrollers like the COPSTM devices this is particularly true as one has a complete computer system in a chip. In order to reduce the testing burden, the facilities to ease the testing have been built into the COPS devices. With the test ability built into the device for production test, the user need only follow set procedures to verify the chip at incoming inspection or field test.

#### 2.0 PHILOSOPHY

The basic test philosophy requires that four major areas be exercised. These areas are:

1) Synchronize the device and tester.

- 2) Test the internal logic and I/O.

- 3) Test the RAM.

- 4) Verify the ROM program.

If the devices perform all of these four properly, the device is good. This is a reasonable assumption with a standard device that has a debugged test routine and is ROM programmed. A custom circuit just going into production might not have the accumulated test background. By attacking the problem on a "sum of the parts" approach, one need not do any exhaustive functional test on routine production parts. This will be a major gain where lengthy time consuming or time dependent routines are involved. If one attempts to do a functional test of the chip, a sequence that is unique to the application is needed. Thus, a test program must be written and debugged for each ROM pattern. Further, a test box/board must be designed, built, debugged, documented, and maintained for each one. If testing has been considered from the beginning, the chip will have built-in capabilities to exercise the various parts of it. The different functional parts and instructions are tested to verify proper operation at the voltage and frequency limits.

#### 3.0 BUILT-IN TEST FEATURES

The first step in testing the COP400 devices is to understand the built-in test control features. This will involve the SI/O and the L lines. The SO pin has been designed to be the control node for testing. The pin will normally be in an active low state and when forced high externally, places the chip in the test mode. It should be noted that this output can sink considerable current and one should not force the pin to the  $V_{CC}$  rail. By limiting the voltage to the 2.0/3.0V range one can not damage the device where the application of a higher voltage could. When forced into the test mode the SI pin controls the sub mode of the chip. With SI high the data placed on the L port is used as an instruction. When SI is low (and the L output is enabled) the contents of the ROM will be dumped out through the L port. Certain other internal functions have been implemented to allow these modes but these are not part of the basic operation. Included in this category is the activation of the skip signal to prevent the program counter from jumping out of sequence by executing a program control instruction.

COPS™ and MICROWIRE™ are trademarks of National Semiconductor Corporation.

© 1995 National Semiconductor Corporation TL/DD/6940

RRD-B30M105/Printed in U. S. A

#### 3.1 Sync Between Tester and DUT

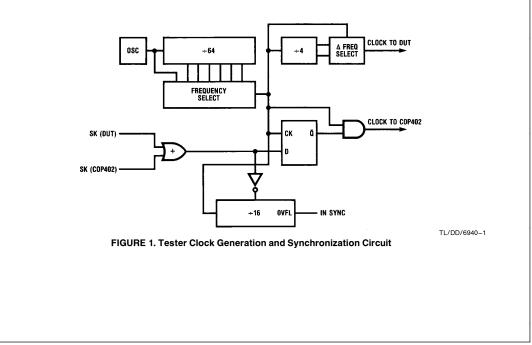

In order to be able to test a COPS chip, the tester must be in sync with the device under test (DUT). By using an external oscillator the two may be run at the same frequency. This is true regardless of the option or type of oscillator chosen for the chip. Even the RC configuration may be overridden with an external signal that meets the level requirements. In addition to running at the same frequency, the chip and tester must be in sync on a bit basis. See *Figure 1*. The supportive features mentioned above include the condition of the SK signal being a bit (instruction) clock until stopped by software in the program. Hence, one can start the tests based on an edge change of SK. It is important that this be accurate because all data I/O changes will be relative to the SK timing (see the appropriate device data sheet).

It should also be noted that the oscillator frequency is programmed to a rate of 4-32 higher than SK. If one is building a test fixture for more than one device, some method must be available to enter this number. If one is testing a COP420 or COP421 near its upper limit it would be wise to do the SK sync operation at a lower rate and then increase the input frequency. This is desirable because the phase relationship is close to TTL propagation delays at the upper limit. Implementation of the area could be a preset counter that is gated on after a zero to one transition is seen on SK. Continual comparison could be made but once in sync, there should not be any need for the comparison as they should remain in sync.

The basic use of this "sync counter" is to derive the proper timing for loading data and instructions into the chip and verify the outputs. The COP402 data sheet should be used as a guide for these times, modified properly for the L and C parts. For those designing testers, it is suggested that one not attempt to test worse case timing changes as these could be very difficult to implement. Like other parametric tests these should in general be left to the professional test equipment.

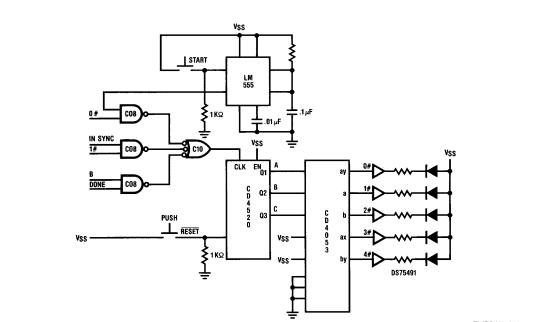

#### 3.2 Internal Logic Test

With the device and the tester in sync, actual testing may begin. See the sequence control circuit of *Figure 2*. To place the chip into the test mode the SO output is pulled to a one level (between 2.0 and 3.0 volts). It should be pulled with a circuit that will limit the upper voltage to 3V as this output can have a significant current sink capability. On power up (or after reset) the SO line is set to a zero by the internal logic. An internal sense line will detect the forced condition and provide test control. A delay of 10 ms should be taken after power-up to allow the power on reset circuit to time out before instructions can be executed. If the reset pin is activated in mid-program for some reason, several instructions cycle times should be ignored to insure complete operation.

The tester should at this point force instructions into the L port. These instructions will be executed as if they were from the ROM. The sequence of the instructions is not particularly critical. Table I gives an example sequence. The main steps are to be able to detect an output change (OGI) early to verify connection/operation. It is much better to find a problem before going through the steps of loading RAM and then finding that the chip doesn't work. All instructions should be exercised although certain ones should be postponed. Enabling the Q register to the L port is an example. This would interfere with the insertion of instructions on the L port. Another problem is the SO test which could be set up with an XAS and then released from the test mode to check proper data output.

Certain commands will require more effort than others. To check the program counter during JMP's and sub-routine operation will require that known info at the new address be available. One should execute a JSRP at some known address and release the test mode to see that the operation in the subroutine (e.g., SC) is done and that a return is made to N + 1. At this point test mode can be re-established to continue the test. The main point to remember is to provide a positive indication of the success of that specific test.

FIGURE 2. Tester Mode Sequencer

TL/DD/6940-2

#### 3.3 RAM Test

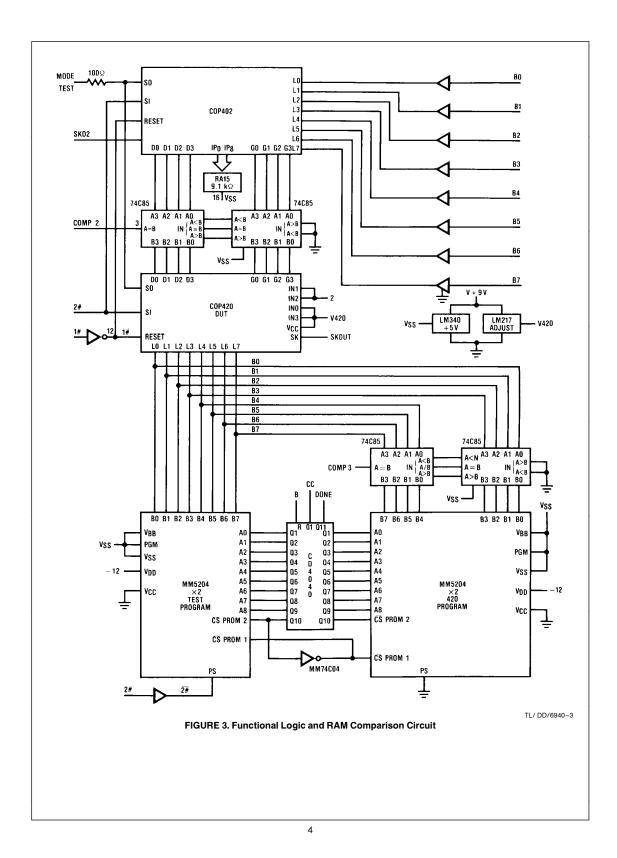

The verification of RAM is a part of the internal logic test, but is treated separately here. One must check both the RAM and its address register to find all faults. An example of this testing would be to load RAM with a string of STII commands. By then going back and reading this data to the outside (through an OMG instruction in a loop) the tester could verify both RAM and address were functional. One could then load RAM with all 6's and 9's (or 5's and 10's) sequentially to insure that all bits were functional and adjacent bits not shorted. Other similar tests could be run at the discretion of the user to do further testing. All of these tests would utilize the output of data via the G ports to validate the data. See the comparator circuit *Figure 3.*

#### 3.4 ROM Dump

Successful operation of the internal logic tests and RAM will lead to the final test phase, ROM comparison. In order to

check the ROM contents, the ROM dump mode must be entered. One should force a JMP to an address near the end of the ROM space (3FF for a 420 chip, 1FF for a 410). A desirable point might be 3FA. The program counter will step ahead on each instruction cycle unless a program control is executed. The next step is to load the Q register with a non-conflicting value so that the enabling of the L outputs will not destroy the second byte of the LEI instruction as control is passed into the ROM dump mode. After going to this address, one should execute an enable of the L lines to the output port (LEI 4). Having done this the external buffers should be disabled and the SI pin taken low. This will allow data out and remove potential level conflicts. By letting the PC step ahead to address zero one can then begin the byte by byte comparison of data. In this mode the controller is not executing the code because the skip line is enabled throughout the sequence. By halting a counter on a failure, one could determine the questionable address.

| INSTRUCTION        | RESULT               | TABLE I. Typical T<br>COMMENTS                              | est Sequence        | RESULT     | COMMENTS                                               |

|--------------------|----------------------|-------------------------------------------------------------|---------------------|------------|--------------------------------------------------------|

| NOP                | NO CHANGE            | CHECK NOP & ALLOW TRANSIENT                                 | CLRA                |            |                                                        |

|                    |                      | CYCLE FOR MODE                                              | ASC                 |            | CHECK ADD WITH CARRY                                   |

| OGI 9<br>OGI 6     | G(0 > 9)<br>G(9 > 6) | NOT ON 410L/411L<br>REVERSE ALL G STATES                    | SC<br>SKC           |            | CHECK SET CARRY<br>CHECK SKIP ON CARRY                 |

| STII 8             | ()                   | SET UP 0,0 FOR FUTURE                                       | LDD 0,0             |            |                                                        |

| LBI 3,13<br>OBD    | D(0 > 13             | B TO NEW POSITION (3, 13)<br>CHECK D                        | X<br>OMG            | G = 9      | STORE A<br>NO CHANGE                                   |

| CLRA               |                      | MAKE SURE $A = 0$                                           | CLRA                |            |                                                        |

| XABR<br>CAB        |                      | 3 > A; 0 > Br<br>MOVE 3 to Bd                               | ASC<br>X            |            |                                                        |

| OBD                | D(13 > 3)            | CHECK XABR CAB & D CHANGE                                   | OMG<br>CAMQ         | G(9 > 10)  | CARRY ADDS ONE TO MEMORY                               |

| CLRA<br>AISC 2     |                      | IFORCE A > 2                                                | XDS                 |            | STORE A & M IN Q; 10,9<br>9 > 3,1; 10 > A; Bd > 3,0    |

| CAB<br>OBD         | D(3 > 2)             | 2 > Bd<br>VERIFY 2 FROM A > Bd                              | X<br>OMG            | G(10 > 9)  | STORE 9 IN 3,0                                         |

| STII 7             |                      | 7 > 0.2 & Bd > 3                                            | LD 2                | G(10 > 3)  | 9 > A; Bd > 1,0                                        |

| OBD<br>CAB         | D(2 > 3)             | STII INCREMENTS Bd<br>SEE THAT A STILL THE SAME             | INSTRUCTION         | RESULT     | COMMENTS                                               |

| OMG                | G(6 > 7)             | OMB & RAM CHECK                                             |                     |            | COMMENTS                                               |

| CLRA<br>CAB        |                      | B(0,0)                                                      | OMG<br>LD 3         | G(9 > 1)   | 1 > A; Bd > 2,0                                        |

| OMG                | G(7 > 8)             | TIE IN RAM, A & G OPERATION                                 | OMG                 | G(1 > 2)   |                                                        |

| SMB 0<br>OMG       | G(8 > 9)             | SMB INST. CHECK                                             | ADD<br>X            |            | ADD WITHOUT CARRY<br>STORE 3 IN 2,0                    |

| SMB 1              | . ,                  | :                                                           | SC                  |            |                                                        |

| OMG<br>RMB 0       | G(9 > 11)            |                                                             | LDD 0,0<br>CASC     |            | 7 > A<br>CHECK CASC                                    |

| RMB 3              |                      | :                                                           | SKC                 |            |                                                        |

| X<br>CAB           |                      | :0 > 0,0;2 > A<br>A = 2 > B                                 | X<br>OMG            | G(2 > 12)  | STORE 12                                               |

| OMG<br>LD 1        | G(11 > 7)            | OUTPUT M(0,2) $M(0,2) > A \cdot B > 1.2$                    | CLRA<br>AISC 3      |            | :                                                      |

| XAD 0,0            |                      | M(0,2) > A; B > 1,2<br>A(7) < -> M(0,0) 2                   | X                   |            | :                                                      |

| AISC 15<br>LDD 0,0 |                      | AISC CHECK; $A = 1$<br>CHECK SKIP OF 2 BYTE INST.           | SC<br>SKC           |            | :CHECK<br>:SKC/SC                                      |

| X                  |                      | STORE 1                                                     | х                   |            | :                                                      |

| OMB<br>LD 0        | G(7 > 1)             | VERIFY<br>COPY1,2 BACK TO A                                 | OMG<br>RC           | G(12 > 3)  |                                                        |

| ADT                |                      | ADD TEN                                                     | SKC                 |            | :CHECK                                                 |

| XDS<br>XDS         |                      | LEAVE 11 IN 1,2;GO 1, 1 WITH 1<br>LEAVE 1 IN 1,1;GO 1,0 W ? | X<br>OMG            | G(3 > 12)  | :RC<br>:                                               |

| OBD                | D(2 > 0)             | CHECK Bd MOVEMENT                                           | LBI 0,0             | - (        | :CHECK                                                 |

| STII 5<br>CBA      |                      | 5 > 1,0;Bd TO 1,1<br>CHECK B > A                            | LBI 1,15<br>LBI 2,7 |            | ;SEQUENTIAL LBI'S<br>ALSO SKIPPED (LBI 2,7 NOT IN 410) |

| AISC 3             |                      | AISC CHECK 4 > A                                            | OMG<br>CQMA         | G(2 > 7)   | LOAD CONSTANTS FROM Q                                  |

| INSTRUCTION        | RESULT               | COMMENTS                                                    | OMG                 | G(7 > 9)   | CHECK                                                  |

| XDS                |                      | 1 > A; 4 > 1,1                                              | X<br>OMG            | G(9 > 10)  | :                                                      |

| OMG                | G(1 > 5)             | FROM 1,0                                                    | LEI 1               | G(0 × 10)  |                                                        |

| XDS<br>LDD 0,0     |                      | 5 > A; 1 > 1,0; Bd < 15 SKIP<br>SKIPPED !                   | XAS<br>CLRA         |            | STORE A $- >$ S (9)                                    |

| OBD                | D(0 > 15)            |                                                             | AISC 7              |            | :                                                      |

| AISC 4<br>X        |                      | 9 > A<br>9 > 15                                             | SKGBZ 0<br>X        |            | :<br>:CHECK                                            |

| OMG<br>CLRA        | G(5> 9)              |                                                             | OMG<br>SKGBZ 1      |            | :                                                      |

| COMP               |                      | ONES TO A                                                   | Х                   |            | :<br>;G BIT                                            |

| XOR<br>XIS         |                      | FLIP MEMORY<br>6 > 1,15; 9 > A; Bd > 1,0                    | OMG<br>SKGBZ 2      | G (10 > 7) | :                                                      |

| LDD 0,0            |                      | SKIP                                                        | х                   |            | :                                                      |

| SKE<br>LB 1,2      |                      | SKIP 2 WORD LBI (NOT IN 410)                                | OMG<br>SKGBZ 3      | G(7 > 10)  | :TESTS                                                 |

| OBD                | D(15 > 0)            | VERIFY WORD                                                 | х                   |            | :                                                      |

| SKE<br>LBI 1,0     |                      | 11 NOT = 9<br>BACK TO 1,0                                   | OMG                 | G(10 > 7)  | :                                                      |

| SMB 2              |                      | :                                                           | INSTRUCTION         | RESULT     | COMMENTS                                               |

| SKE<br>RMB 2       |                      | :                                                           | SKGZ                |            |                                                        |

| SKE<br>SMB 3       |                      | :CHECK BIT<br>:MANIPULATIONS                                | X<br>OMG            | G(7 > 10)  | :CHECK<br>:                                            |

| SKE                |                      | :                                                           | OGI 0               | G(10 > 0)  | :G TEST                                                |

| LDD 0,0<br>X 3     |                      | :<br>Bd > 2,0                                               | SKGZ<br>X           |            | :                                                      |

| XAD 1,1<br>XIS 1   |                      | 9 > 1,1; 4 > A<br>4 > 2,0; Bd > 3,1                         | OMG<br>SKMBZ 0      | G(0 > 10)  | :                                                      |

| ING                |                      | INPUT G PORT                                                | Х                   |            | CHECK MEMORY BIT TESTS                                 |

| X                  |                      | STORE                                                       | OMG<br>SKMBZ 1      |            | NO CHANGE                                              |

|                    |                      |                                                             |                     |            |                                                        |

| INSTRUCTION                                                                                                          | RESULT    | TABLE I. Typical Test<br>COMMENTS            | t Sequence (Continued)<br>INSTRUCTION                                 | RESULT | COMMENTS                                                                                                    |

|----------------------------------------------------------------------------------------------------------------------|-----------|----------------------------------------------|-----------------------------------------------------------------------|--------|-------------------------------------------------------------------------------------------------------------|

| X<br>OMG                                                                                                             | G(10 > 7) | NO SKIP                                      | STII 2<br>STII 9                                                      |        |                                                                                                             |

| SKMBZ 2                                                                                                              | G(10 × 1) |                                              | STIL 0                                                                |        |                                                                                                             |

| Х                                                                                                                    |           | WON'T SKIP                                   | LBI 3,0                                                               |        |                                                                                                             |

| OMG                                                                                                                  | G(7 > 10) |                                              | STIL 7                                                                |        |                                                                                                             |

| INIL<br>ININ                                                                                                         |           | SEE THAT L LATCHES RESET<br>ASSUME G $- > I$ | STII 14<br>STII 5                                                     |        |                                                                                                             |

| SKE                                                                                                                  |           |                                              | STII 12                                                               |        |                                                                                                             |

| X1                                                                                                                   |           | Br > 1                                       | STIL 3                                                                |        |                                                                                                             |

| OMG                                                                                                                  |           | SHOULD BE EQUAL                              | STII 10                                                               |        |                                                                                                             |

| INIL                                                                                                                 |           | :                                            | STII 1                                                                |        |                                                                                                             |

| X<br>SKMBZ 3                                                                                                         |           |                                              | STII 8<br>STII 15                                                     |        |                                                                                                             |

| OBD                                                                                                                  | D(15 > 0) | :INIL TEST                                   | STIL 6                                                                |        |                                                                                                             |

| OGI 1                                                                                                                | D(10 / 0) | :                                            | STII 13                                                               |        |                                                                                                             |

| LBI 3,11                                                                                                             |           | :                                            | STII 4                                                                |        |                                                                                                             |

| OGI 0                                                                                                                |           | :                                            | STII 11                                                               |        |                                                                                                             |

| INIL                                                                                                                 |           | :                                            | STIL 2                                                                |        |                                                                                                             |

| X<br>SKMBZ 0                                                                                                         |           |                                              | STII 9<br>STII 0                                                      |        |                                                                                                             |

| OBD                                                                                                                  | D(0 > 11) |                                              | 3110                                                                  |        |                                                                                                             |

| NOP                                                                                                                  | -(,       |                                              | INSTRUCTION                                                           | RESULT | COMMENTS                                                                                                    |

| XAS                                                                                                                  |           | :                                            |                                                                       |        |                                                                                                             |

| X                                                                                                                    | 0/10      | :XAS TEST                                    | LBI 0,0                                                               |        | CHECK FOR RAM DATA                                                                                          |

| OMG                                                                                                                  | G(10 > 9) | :                                            | OMG<br>LD                                                             |        | OUTPUT DATA                                                                                                 |

| INSTRUCTION                                                                                                          | RESULT    | COMMENTS                                     | XIS                                                                   |        | :<br>:MOVE TO NEXT DIGIT                                                                                    |

|                                                                                                                      | HEODE1    | COMMENTO                                     | OMG                                                                   |        | OUTPUT DATA                                                                                                 |

| LBI 0,0                                                                                                              |           | LOAD RAM WITH                                | LD                                                                    |        | :                                                                                                           |

| STII 7                                                                                                               |           | CONSTANTS USING                              | XIS                                                                   |        | :MOVE TO NEXT DIGIT                                                                                         |

| STII 14                                                                                                              |           | STII                                         | OMG                                                                   |        | OUTPUT DATA                                                                                                 |

| STII 5<br>STII 12                                                                                                    |           |                                              | LD<br>XIS                                                             |        | :<br>:MOVE TO NEXT DIGIT                                                                                    |

| STIL3                                                                                                                |           |                                              | OMG                                                                   |        | OUTPUT DATA                                                                                                 |

| STII 10                                                                                                              |           |                                              | LD                                                                    |        | :                                                                                                           |

| STII 1                                                                                                               |           |                                              | XIS                                                                   |        | :MOVE TO NEXT DIGIT                                                                                         |

| STIL8                                                                                                                |           |                                              | OMG                                                                   |        | OUTPUT DATA                                                                                                 |

| STII 15<br>STII 6                                                                                                    |           |                                              | LD<br>XIS                                                             |        | :<br>:MOVE TO NEXT DIGIT                                                                                    |

| STII 13                                                                                                              |           |                                              | OMG                                                                   |        | OUTPUT DATA                                                                                                 |

| STII 4                                                                                                               |           |                                              | LD                                                                    |        | :                                                                                                           |

| STII 11                                                                                                              |           |                                              | XIS                                                                   |        | :MOVE TO NEXT DIGIT                                                                                         |

| STIL2                                                                                                                |           |                                              | OMG                                                                   |        | OUTPUT DATA                                                                                                 |

| STII 9<br>STII 0                                                                                                     |           |                                              | LD<br>XIS                                                             |        | :<br>:MOVE TO NEXT DIGIT                                                                                    |

| LBI 1,0                                                                                                              |           |                                              | OMG                                                                   |        | OUTPUT DATA                                                                                                 |

| STIL7                                                                                                                |           |                                              | LD                                                                    |        | :                                                                                                           |

| STII 14                                                                                                              |           |                                              | XIS                                                                   |        | :MOVE TO NEXT DIGIT                                                                                         |

| STIL 5                                                                                                               |           |                                              | OMG                                                                   |        | OUTPUT DATA                                                                                                 |

| STII 12<br>STII 3                                                                                                    |           |                                              | LD<br>XIS                                                             |        | :<br>:MOVE TO NEXT DIGIT                                                                                    |

| STII 10                                                                                                              |           |                                              | OMG                                                                   |        | OUTPUT DATA                                                                                                 |

| STII 1                                                                                                               |           |                                              | LD                                                                    |        | :                                                                                                           |

| STII 8                                                                                                               |           |                                              | XIS                                                                   |        | :MOVE TO NEXT DIGIT                                                                                         |

| STIL 15                                                                                                              |           |                                              | OMG                                                                   |        | OUTPUT DATA                                                                                                 |

| STII 6<br>STII 13                                                                                                    |           |                                              | LD<br>XIS                                                             |        | :<br>:MOVE TO NEXT DIGIT                                                                                    |

| STIL4                                                                                                                |           |                                              | OMG                                                                   |        | OUTPUT DATA                                                                                                 |

| STII 11                                                                                                              |           |                                              | LD                                                                    |        | :                                                                                                           |

| STII 2                                                                                                               |           |                                              | XIS                                                                   |        | :MOVE TO NEXT DIGIT                                                                                         |

| STII 9                                                                                                               |           |                                              | OMG                                                                   |        | OUTPUT DATA                                                                                                 |

| STII 0<br>LBI 2,0                                                                                                    |           |                                              | LD<br>XIS                                                             |        | :<br>:MOVE TO NEXT DIGIT                                                                                    |

| STIL7                                                                                                                |           |                                              | OMG                                                                   |        | OUTPUT DATA                                                                                                 |

| STII 14                                                                                                              |           |                                              | LD                                                                    |        | :                                                                                                           |

|                                                                                                                      |           |                                              | VIO                                                                   |        | :MOVE TO NEXT DIGIT                                                                                         |

| STII 5                                                                                                               |           |                                              | XIS                                                                   |        |                                                                                                             |

| STII 5<br>STII 12                                                                                                    |           |                                              | OMG                                                                   |        | OUTPUT DATA                                                                                                 |

| STII 5<br>STII 12<br>STII 3                                                                                          |           |                                              | OMG<br>LD                                                             |        | :                                                                                                           |

| STII 5<br>STII 12                                                                                                    |           |                                              | OMG                                                                   |        | OUTPUT DATA<br>:<br>:MOVE TO NEXT DIGIT<br>OUTPUT DATA                                                      |

| STII 5<br>STII 12<br>STII 3<br>STII 10<br>STII 1<br>STII 8                                                           |           |                                              | omg<br>Ld<br>XIS<br>Omg<br>LD                                         |        | :<br>:MOVE TO NEXT DIGIT<br>OUTPUT DATA<br>:                                                                |

| STII 5<br>STII 12<br>STII 3<br>STII 10<br>STII 10<br>STII 1<br>STII 8<br>STII 15<br>STII 6                           |           |                                              | OMG<br>LD<br>XIS<br>OMG<br>LD<br>XIS                                  |        | :<br>MOVE TO NEXT DIGIT<br>OUTPUT DATA<br>:<br>MOVE TO NEXT DIGIT                                           |

| STII 5<br>STII 12<br>STII 3<br>STII 10<br>STII 10<br>STII 15<br>STII 6<br>STII 13                                    |           |                                              | OMG<br>LD<br>XIS<br>OMG<br>LD<br>XIS<br>INSTRUCTION                   | RESULT | MOVE TO NEXT DIGIT<br>OUTPUT DATA<br>:<br>MOVE TO NEXT DIGIT<br>COMMENTS                                    |

| STII 5<br>STII 12<br>STII 3<br>STII 10<br>STII 10<br>STII 1<br>STII 8<br>STII 15<br>STII 6<br>STII 13<br>INSTRUCTION | RESULT    | COMMENTS                                     | OMG<br>LD<br>XIS<br>OMG<br>LD<br>XIS<br>INSTRUCTION<br>LBI 1,0<br>OMG | RESULT | :<br>MOVE TO NEXT DIGIT<br>OUTPUT DATA<br>:<br>MOVE TO NEXT DIGIT                                           |

| STII 5<br>STII 12<br>STII 3<br>STII 10<br>STII 10<br>STII 15<br>STII 6<br>STII 13                                    | RESULT    | COMMENTS                                     | OMG<br>LD<br>XIS<br>OMG<br>LD<br>XIS<br>INSTRUCTION<br>LBI 1,0        | RESULT | :<br>MOVE TO NEXT DIGIT<br>OUTPUT DATA<br>:<br>:MOVE TO NEXT DIGIT<br><b>COMMENTS</b><br>CHECK FOR RAM DATA |

| INSTRUCTION            | RESULT | TABLE I. Typical Test<br>COMMENTS  | Sequence (Continued)<br>INSTRUCTION | RESULT    | COMMENTS               |

|------------------------|--------|------------------------------------|-------------------------------------|-----------|------------------------|

| OMG                    |        | OUTPUT DATA                        | OMG                                 |           | OUTPUT DATA            |

| LD                     |        |                                    | LD                                  |           |                        |

| XIS                    |        | :MOVE TO NEXT DIGIT                | XIS                                 |           | :MOVE TO NEXT DIGI     |

| OMG                    |        | OUTPUT DATA                        | OMG                                 |           | OUTPUT DATA            |

| _D                     |        | :                                  | LD                                  |           | :                      |

| KIS                    |        | :MOVE TO NEXT DIGIT                | XIS                                 |           | :MOVE TO NEXT DIGI     |

| DMG                    |        | OUTPUT DATA                        | OMG                                 |           | OUTPUT DATA            |

| D                      |        | :                                  | LD                                  |           | :                      |

| KIS                    |        | :MOVE TO NEXT DIGIT                | XIS                                 |           | :MOVE TO NEXT DIGI     |

| ĴMG                    |        | OUTPUT DATA                        | OMG                                 |           | OUTPUT DATA            |

| D                      |        |                                    | LD                                  |           |                        |

| (IS                    |        | :MOVE TO NEXT DIGIT                | XIS                                 |           | :MOVE TO NEXT DIGI     |

| OMG                    |        | OUTPUT DATA                        | OMG                                 |           | OUTPUT DATA            |

|                        |        | OUTFOILDATA                        |                                     |           | OUTFUT DATA            |

| D                      |        |                                    | LD                                  |           |                        |

| KIS                    |        | :MOVE TO NEXT DIGIT                | XIS                                 |           | :MOVE TO NEXT DIGI     |

| DMG                    |        | OUTPUT DATA                        | OMG                                 |           | OUTPUT DATA            |

| D                      |        | :                                  | LD                                  |           | :                      |

| (IS                    |        | :MOVE TO NEXT DIGIT                | XIS                                 |           | :MOVE TO NEXT DIGI     |

| DMG                    |        | OUTPUT DATA                        |                                     |           |                        |

| D                      |        | :                                  | INSTRUCTION                         | RESULT    | COMMENTS               |

| (IS                    |        | MOVE TO NEXT DIGIT                 |                                     |           |                        |

| OMG                    |        | OUTPUT DATA                        | LBI 3,0                             |           | CHECK FOR RAM DA       |

| .D                     |        | ·                                  | OMG                                 |           | OUTPUT DATA            |

|                        |        |                                    |                                     |           |                        |

| (IS                    |        | :MOVE TO NEXT DIGIT                | LD                                  |           |                        |

| DMG                    |        | OUTPUT DATA                        | XIS                                 |           | :MOVE TO NEXT DIGI     |

| D                      |        | :                                  | OMG                                 |           | OUTPUT DATA            |

| (IS                    |        | :MOVE TO NEXT DIGIT                | LD                                  |           | :                      |

| DMG                    |        | OUTPUT DATA                        | XIS                                 |           | :MOVE TO NEXT DIGI     |

| D                      |        | :                                  | OMG                                 |           | OUTPUT DATA            |

| (IS                    |        | :MOVE TO NEXT DIGIT                | LD                                  |           | :                      |

| DMG                    |        | OUTPUT DATA                        | XIS                                 |           | :MOVE TO NEXT DIGI     |

| D                      |        |                                    | OMG                                 |           | OUTPUT DATA            |

| (IS                    |        | :MOVE TO NEXT DIGIT                | LD                                  |           |                        |

| OMG                    |        |                                    | XIS                                 |           | :MOVE TO NEXT DIGI     |

|                        |        | OUTPUT DATA                        |                                     |           |                        |

| D                      |        |                                    | OMG                                 |           | OUTPUT DATA            |

| KIS                    |        | :MOVE TO NEXT DIGIT                | LD                                  |           | :                      |

| DMG                    |        | OUTPUT DATA                        | XIS                                 |           | :MOVE TO NEXT DIGI     |

| D                      |        | :                                  | OMG                                 |           | OUTPUT DATA            |

| KIS                    |        | :MOVE TO NEXT DIGIT                | LD                                  |           | :                      |

| DMG                    |        | OUTPUT DATA                        | XIS                                 |           | :MOVE TO NEXT DIGI     |

| D                      |        | :                                  | OMG                                 |           | OUTPUT DATA            |

| (IS                    |        | :MOVE TO NEXT DIGIT                | LD                                  |           | :                      |

| OMG                    |        | OUTPUT DATA                        | XIS                                 |           | :MOVE TO NEXT DIGI     |

| D                      |        |                                    | OMG                                 |           | OUTPUT DATA            |

| (IS                    |        | :MOVE TO NEXT DIGIT                | LD                                  |           |                        |

|                        |        | NOVE TO NEXT DIGIT                 | XIS                                 |           | :MOVE TO NEXT DIGI     |

| NSTRUCTION             | RESULT | COMMENTS                           | OMG                                 |           | OUTPUT DATA            |

| NSTRUCTION             | RESULT | COMMENTS                           |                                     |           | OUTFUT DATA            |

|                        |        |                                    | LD                                  |           |                        |

| _BI 1,0                |        | CHECK FOR RAM DATA                 | XIS                                 |           | :MOVE TO NEXT DIGI     |

| DMG                    |        | OUTPUT DATA                        | OMG                                 |           | OUTPUT DATA            |

| D                      |        | :                                  | LD                                  |           | :                      |

| (IS                    |        | :MOVE TO NEXT DIGIT                | XIS                                 |           | :MOVE TO NEXT DIGI     |

| DMG                    |        | OUTPUT DATA                        | OMG                                 |           | OUTPUT DATA            |

| .D                     |        | :                                  | LD                                  |           | :                      |

| (IS                    |        | :MOVE TO NEXT DIGIT                | XIS                                 |           | :MOVE TO NEXT DIGI     |

| DMG                    |        | OUTPUT DATA                        | OMG                                 |           | OUTPUT DATA            |

| D                      |        | :                                  | LD                                  |           | :                      |

| (IS                    |        | :MOVE TO NEXT DIGIT                | XIS                                 |           | :MOVE TO NEXT DIGI     |

| DMG                    |        | OUTPUT DATA                        | OMG                                 |           | OUTPUT DATA            |

| .D                     |        | ·                                  | LD                                  |           |                        |

| (IS                    |        | :MOVE TO NEXT DIGIT                | XIS                                 |           | :<br>MOVE TO NEXT DIGI |

|                        |        |                                    |                                     |           | OUTPUT DATA            |

| DMG                    |        | OUTPUT DATA                        | OMG                                 |           | OUIPUI DATA            |

| D                      |        |                                    | LD                                  |           |                        |

| (IS                    |        | :MOVE TO NEXT DIGIT                | XIS                                 |           | :MOVE TO NEXT DIGI     |

| DMG                    |        | OUTPUT DATA                        | OMG                                 |           | OUTPUT DATA            |

| D                      |        | :                                  | LD                                  |           | :                      |

| (IS                    |        | :MOVE TO NEXT DIGIT                | XIS                                 |           | :MOVE TO NEXT DIGI     |

| OMG                    |        | OUTPUT DATA                        | OMG                                 |           | OUTPUT DATA            |

| D                      |        | :                                  | LD                                  |           | :                      |

| (IS                    |        | MOVE TO NEXT DIGIT                 | XIS                                 |           | :MOVE TO NEXT DIGI     |

| OMG                    |        | OUTPUT DATA                        | 710<br>710                          |           |                        |

| _D                     |        |                                    | INSTRUCTION                         | DECULT    | COMMENTS               |

|                        |        | :<br>MOVE TO NEXT DIGIT            | INSTRUCTION                         | RESULT    | COMMENTS               |

| (IS                    |        |                                    |                                     |           |                        |

| DMG                    |        | OUTPUT DATA                        | JMP X                               |           | -SELECT ADDRESS X      |

|                        |        | :                                  |                                     |           | R OMG (SELECT LBI      |

|                        |        |                                    |                                     |           |                        |

| KIS                    |        | :MOVE TO NEXT DIGIT                |                                     | FOR KNOW  |                        |

| KIS                    |        | :MOVE TO NEXT DIGIT<br>OUTPUT DATA | RELEASE TEST MODE                   | OBD (SELE | CT B FOR KNOWN         |

| LD<br>KIS<br>DMG<br>LD |        |                                    | RELEASE TEST MODE                   | OBD (SELE |                        |

| INSTRUCTION<br>SET TEST MODE<br>JP X-2<br>JSR Y                   | RESULT COMMENTS                                                                             | test routine and is only shown as an example of what<br>be done to test various COPS parts. It is also advise<br>approach measurements in the test mode with som<br>tion. As stated earlier, one can force a large current in |

|-------------------------------------------------------------------|---------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| RELEASE TEST MODE                                                 | "Y" SHOULD CHANGE THE OUTPUT<br>CONDITIONS OF "X"                                           | SO node to place the chip in the test mode. Not or<br>this current do damage if unlimited, but it can also                                                                                                                    |

| EXECUTE CODE (Y)<br>SET TEST MODE<br>RET                          | IF AT ALL POSSIBLE                                                                          | local current overloading such that some I/O con<br>may be adversely affected. Obviously this will be mo                                                                                                                      |

| RELEASE TEST MODE<br>EXECUTE "X" AGAIN<br>SET TEST MODE<br>JP X-2 | VERIFIES RET                                                                                | nounced at higher $V_{CC}$ voltages. A specific example the L output current sink test should only be tester $V_{OUT}$ of 0.4V and 0.36 mA as the more stringent test                                                         |

| JSRP Z<br>RELEASE TEST MODE                                       | CHECK JSRP & RETSK                                                                          | exceed power limits when combined with the SO cur                                                                                                                                                                             |

| EXECUTE CODE                                                      | "Z" SHOULD CHANGE "X"<br>OUTPUT CONDITIONS                                                  | MICROWIRE™<br>National's super-sensible MICROWIRE serial da                                                                                                                                                                   |

| SET TEST MODE<br>RETSK                                            | DON'T CHANGE Z CONDITIONS —<br>RETSK                                                        | change standard allows interfacing to any number of<br>cialized peripherals using an absolute minimum num<br>valuable 1/0 piper this leaves more 1/0 lines available                                                          |

| RELEASE TEST MODE<br>EXECUTE                                      |                                                                                             | valuable I/O pins; this leaves more I/O lines availa<br>system interfacing and/or may permit the COPS con                                                                                                                     |

| SET TEST MODE<br>LOAD A & M TO                                    | FIND VALUE OF ADDRESS IN BLOCK                                                              | to be packaged in a smaller (and even lower cost) pa                                                                                                                                                                          |

| VALUE OF ADDRESS                                                  | (4 PAGES)<br>AT OR JUST BEFORE AN OUTPUT                                                    | (MICROWIRE peripherals may also be used with non-<br>controllers). For further applications information, re<br>COPS Briefs 8 and 9. MICROWIRE makes sense.                                                                    |

| TO GO TO<br>OUTPUT CHANGE                                         | CHANGE SET A & M TO ADDRESS<br>OF "VALUE"                                                   | The example below illustrates the power and versa                                                                                                                                                                             |

| JID<br>RELEASE TEST MODE<br>EXECUTE OUTPUT                        | CHECKS JID                                                                                  | MICROWIRE via an extreme example—using one o<br>type of peripheral with a single controller.                                                                                                                                  |

| SET TEST MODE<br>LOAD A & M                                       | LOAD A & M WITH A UNIQUE ADDRESS<br>SUCH THAT CONTENTS OF THAT<br>ADDRESS WILL BE SEEN ON G |                                                                                                                                                                                                                               |

| LQID<br>X064                                                      | ;OR USE THIS CAUSE THE DATA COMES<br>;FROM YOUR TESTER ANYWAY                               |                                                                                                                                                                                                                               |

| CQMA<br>OMG<br>X                                                  | LQUID & CQMA CHECKED                                                                        |                                                                                                                                                                                                                               |

| OMG                                                               | ۰۰<br>-                                                                                     |                                                                                                                                                                                                                               |

| INL<br>OMG                                                        | G - > 2 INL TEST (COPY OF 2nd BYTE)                                                         |                                                                                                                                                                                                                               |

| X<br>OMG                                                          | G - > E :                                                                                   |                                                                                                                                                                                                                               |

|                                                                   | ANALOG CCS DO<br>NTERFACE                                                                   | DI<br>COP472<br>SK C3<br>DI<br>COP472<br>SK C3<br>DI<br>DI<br>DI<br>DI<br>DI<br>DI<br>DI<br>DI<br>DI<br>DI                                                                                                                    |

|                                                                   | DISPLAY                                                                                     | •00 <u>CS</u><br>TL/DD/6940-                                                                                                                                                                                                  |

#### COP431 SERIES, 8-BIT A/D CONVERTERS

The COP431 series is an 8-bit successive approximation A/D converter with a serial I/O and configurable input multiplexer with up to 8 channels. The serial I/O is configured to comply with the NSC MICROWIRE serial data exchange standard for easy interface to the COPS family of processors, and can interface with standard shift registers or other µPs.

The 2, 4 or 8 channel multiplexers are software configured for single-ended or differential inputs as well as channel assignment.

The differential analog voltage input allows increasing the common-mode rejection and offsetting the analog zero input voltage value. In addition, the voltage reference input can be adjusted to allow encoding any smaller analog voltage span to the full 8 bits of resolution.

#### COP472-3 LIQUID CRYSTAL DISPLAY CONTROLLER

The COP472-3 Liquid Crystal Display (LCD) Controller drives a multiplexed liquid crystal display directly. Data is loaded serially and is held in internal latches. The COP472-3 contains an on-chip oscillator and generates all the multilevel waveforms for backplanes and segment outputs on a triplex display. One COP472-3 can drive 36 segments multiplexed as  $3 \times 12$  (4½ digit display). Two COP472-3 devices can be used together to drive 72 segments ( $3 \times 24$ ) which could be an 8½ digit display.

### NM93C06A 256-BIT SERIAL ELECTRICALLY ERASABLE PROGRAMMABLE MEMORY

The NM93C06A is a 256-bit non-volatile memory. The device contains 256 bits of read/write memory divided into 16 registers of 16 bits each. Each register is serially read or written by the COP400 Family Controller. Written information is stored in a floating gate cell with at least 10 years of retention.

#### LIFE SUPPORT POLICY

NATIONAL'S PRODUCTS ARE NOT AUTHORIZED FOR USE AS CRITICAL COMPONENTS IN LIFE SUPPORT DEVICES OR SYSTEMS WITHOUT THE EXPRESS WRITTEN APPROVAL OF THE PRESIDENT OF NATIONAL SEMICONDUCTOR CORPORATION. As used herein:

- Life support devices or systems are devices or systems which, (a) are intended for surgical implant into the body, or (b) support or sustain life, and whose failure to perform, when properly used in accordance with instructions for use provided in the labeling, can be reasonably expected to result in a significant injury to the user.

- 2. A critical component is any component of a life support device or system whose failure to perform can be reasonably expected to cause the failure of the life support device or system, or to affect its safety or effectiveness.

| National Semiconductor<br>Corporation<br>1111 West Bardin Road | National Semiconductor<br>Europe<br>Fax: (+49) 0-180-530 85 86    | National Semiconductor<br>Hong Kong Ltd.<br>13th Floor, Straight Block, | National Semiconductor<br>Japan Ltd.<br>Tel: 81-043-299-2309 |

|----------------------------------------------------------------|-------------------------------------------------------------------|-------------------------------------------------------------------------|--------------------------------------------------------------|

| Arlington, TX 76017                                            | Email: cnjwge@tevm2.nsc.com<br>Deutsch Tel: (+49) 0-180-530 85 85 | Ocean Centre, 5 Canton Rd.                                              | Fax: 81-043-299-2408                                         |

| Tel: 1(800) 272-9959<br>Fax: 1(800) 737-7018                   | English Tel: (+49) 0-180-530 85 85                                | Tsimshatsui, Kowloon<br>Hong Kong                                       |                                                              |

| 1 4. 1(000) 101-1010                                           | Français Tel: (+49) 0-180-532 93 58                               | Tel: (852) 2737-1600                                                    |                                                              |

|                                                                | Italiano Tel: (+49) 0-180-534 16 80                               | Fax: (852) 2736-9960                                                    |                                                              |

National does not assume any responsibility for use of any circuitry described, no circuit patent licenses are implied and National reserves the right at any time without notice to change said circuitry and specifications.

#### **IMPORTANT NOTICE**

Texas Instruments Incorporated and its subsidiaries (TI) reserve the right to make corrections, modifications, enhancements, improvements, and other changes to its products and services at any time and to discontinue any product or service without notice. Customers should obtain the latest relevant information before placing orders and should verify that such information is current and complete. All products are sold subject to TI's terms and conditions of sale supplied at the time of order acknowledgment.

TI warrants performance of its hardware products to the specifications applicable at the time of sale in accordance with TI's standard warranty. Testing and other quality control techniques are used to the extent TI deems necessary to support this warranty. Except where mandated by government requirements, testing of all parameters of each product is not necessarily performed.

TI assumes no liability for applications assistance or customer product design. Customers are responsible for their products and applications using TI components. To minimize the risks associated with customer products and applications, customers should provide adequate design and operating safeguards.

TI does not warrant or represent that any license, either express or implied, is granted under any TI patent right, copyright, mask work right, or other TI intellectual property right relating to any combination, machine, or process in which TI products or services are used. Information published by TI regarding third-party products or services does not constitute a license from TI to use such products or services or a warranty or endorsement thereof. Use of such information may require a license from a third party under the patents or other intellectual property of the third party, or a license from TI under the patents or other intellectual property of TI.

Reproduction of TI information in TI data books or data sheets is permissible only if reproduction is without alteration and is accompanied by all associated warranties, conditions, limitations, and notices. Reproduction of this information with alteration is an unfair and deceptive business practice. TI is not responsible or liable for such altered documentation. Information of third parties may be subject to additional restrictions.

Resale of TI products or services with statements different from or beyond the parameters stated by TI for that product or service voids all express and any implied warranties for the associated TI product or service and is an unfair and deceptive business practice. TI is not responsible or liable for any such statements.

TI products are not authorized for use in safety-critical applications (such as life support) where a failure of the TI product would reasonably be expected to cause severe personal injury or death, unless officers of the parties have executed an agreement specifically governing such use. Buyers represent that they have all necessary expertise in the safety and regulatory ramifications of their applications, and acknowledge and agree that they are solely responsible for all legal, regulatory and safety-related requirements concerning their products and any use of TI products in such safety-critical applications, notwithstanding any applications-related information or support that may be provided by TI. Further, Buyers must fully indemnify TI and its representatives against any damages arising out of the use of TI products in such safety-critical applications.

TI products are neither designed nor intended for use in military/aerospace applications or environments unless the TI products are specifically designated by TI as military-grade or "enhanced plastic." Only products designated by TI as military-grade meet military specifications. Buyers acknowledge and agree that any such use of TI products which TI has not designated as military-grade is solely at the Buyer's risk, and that they are solely responsible for compliance with all legal and regulatory requirements in connection with such use.

TI products are neither designed nor intended for use in automotive applications or environments unless the specific TI products are designated by TI as compliant with ISO/TS 16949 requirements. Buyers acknowledge and agree that, if they use any non-designated products in automotive applications, TI will not be responsible for any failure to meet such requirements.

Following are URLs where you can obtain information on other Texas Instruments products and application solutions:

| Products               |                                 | Applications                  |                                   |

|------------------------|---------------------------------|-------------------------------|-----------------------------------|

| Audio                  | www.ti.com/audio                | Communications and Telecom    | www.ti.com/communications         |

| Amplifiers             | amplifier.ti.com                | Computers and Peripherals     | www.ti.com/computers              |

| Data Converters        | dataconverter.ti.com            | Consumer Electronics          | www.ti.com/consumer-apps          |

| DLP® Products          | www.dlp.com                     | Energy and Lighting           | www.ti.com/energy                 |

| DSP                    | dsp.ti.com                      | Industrial                    | www.ti.com/industrial             |

| Clocks and Timers      | www.ti.com/clocks               | Medical                       | www.ti.com/medical                |

| Interface              | interface.ti.com                | Security                      | www.ti.com/security               |

| Logic                  | logic.ti.com                    | Space, Avionics and Defense   | www.ti.com/space-avionics-defense |

| Power Mgmt             | power.ti.com                    | Transportation and Automotive | www.ti.com/automotive             |

| Microcontrollers       | microcontroller.ti.com          | Video and Imaging             | www.ti.com/video                  |

| RFID                   | www.ti-rfid.com                 |                               |                                   |

| OMAP Mobile Processors | www.ti.com/omap                 |                               |                                   |

| Wireless Connectivity  | www.ti.com/wirelessconnectivity |                               |                                   |

|                        |                                 | u Hama Dawa                   | a O a Al a a m                    |

**TI E2E Community Home Page**

e2e.ti.com

Mailing Address: Texas Instruments, Post Office Box 655303, Dallas, Texas 75265 Copyright © 2011, Texas Instruments Incorporated